La Guerra de la Miniaturización de los Chips

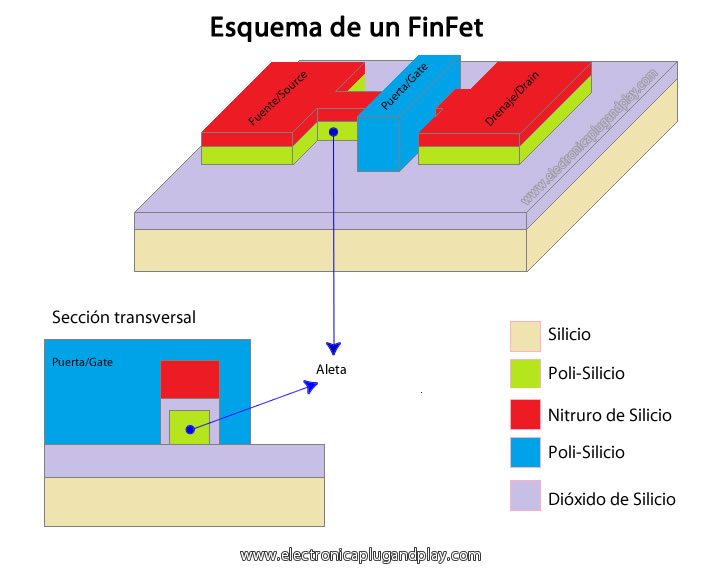

Intel comenzará a fabricar chips de 10nm este año y afirma que liderará la industria de la densidad de transistores usando una métrica que desafió a adoptar a sus rivales. Por otro lado, anunció un nodo FinFET de baja potencia de 22 nm para competir por el negocio de fundición de silicio completamente agotado sobre aislante (FD-SOI) de rivales como Globalfoundries.

A 10nm, Intel empaquetará 100.8 millones de transistores por milímetro cuadrado. Se estima que procesos de fundición de 10nm ahora en producción por parte de compañias como TSMC y Samsung tienen alrededor de la mitad de esa densidad.

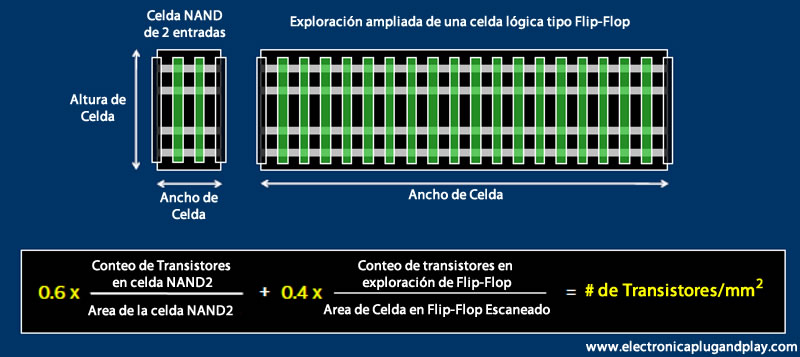

La métrica de Intel promedia la densidad de celdas lógicas pequeñas y grandes. Específicamente, utiliza una celda NAND de dos entradas con dos compuertas activas y una celda de biestable de exploración con hasta 25 compuertas activas.

"Creo que es una métrica comprensiva, cuantitativa y honesta", dijo Mark Bohr, investigador y director de arquitectura de procesos e integración de Intel. "TSMC y, creo, Samsung solían mencionarlo, pero supongo que ya no estaban muy bien con esta métrica", dijo.

La métrica existente de multiplicar el pitch de Gate (Compuerta) y la altura de la celda da un avance relativo entre los nodos, en lugar de un número absoluto de la capacidad de un nodo. Además, no incluye una variedad de factores abarcados por la métrica de densidad propuesta por Intel, agrega Bohr.

Ecuación para el cálculo de la densidad de transistores.

Cualquiera que sea la métrica, Intel anunció que comenzará a fabricar chips Cannonlake de 10nm en la segunda mitad de este año 2017, tres años después de lanzar su proceso de 14nm. Se espera que continúe una cadencia de tres años, estirando 10nm con dos mejoras anuales que se llamarán 10+ y 10++.

No olvides dejarnos tus comentarios en nuestras redes sociales y regalarlos un "me gusta" o +1.

www.electronicaplugandplay.com

Mayo 8, 2017